AXI4 Scatter-Gather DMA Controller IP– Memory-Map Data Transfers

The AXI4 Scatter-Gather (SG) Direct Memory Access (DMA) Controller with Master AXI4 Interconnect (verilog IP core DB-DMAC-MC-AMBA) offers RTL SystemVerilog parameter configurable number of DMA Channels. Alternatively, we offer RTL Verilog releases with fixed 2, 4, 8, and 16 DMA Channels (verilog IP core DB-DMAC-MC-AXI) at lower licensing cost.

Each DMA Channel contains a Scatter-Gather, descriptor-driven unit controlling the data transfer between memory subsystem(s) or between memory and a peripheral. The AXI DMA Controller IP excels at high data throughput at low latency on both small and large data sets.

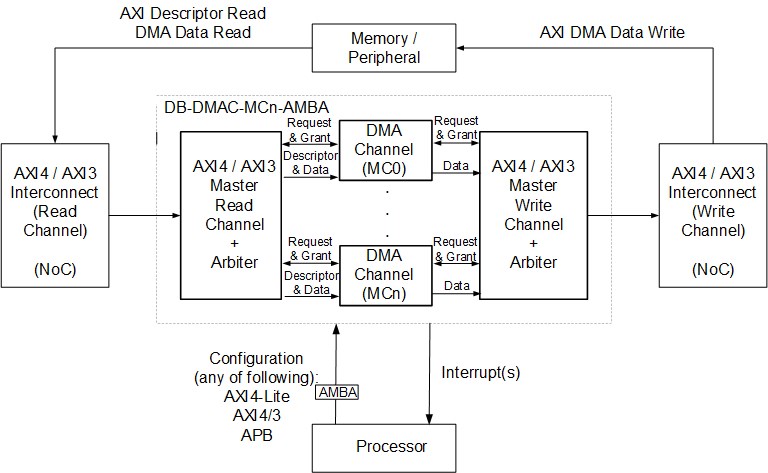

Below is a high-level Microarchitecture view of the AXI4 DMA Controller.

The AXI4 DMA Controller features Scatter-Gather capability, with per channel Finite State Control and single- or dual-clock FIFOs (parameterized in depth and width), interrupt controller, and optional data parity or CRC generator & checker. Both AXI4 and AXI3 AMBA interconnects are available. The AXI Master data Interface scales from 32- to 1024-bits, with programmable data bursts of 1, 4, 8, 16 words (with the smallest data transfer supported is 1 byte), and up to AXI3 16 outstanding read requests, and for AXI4, the availability of programmable QoS and longer data burst lengths up to 256. The AXI DMA Controller also provides a AMBA Slave Interface of a full AXI4, AXI4-lite, AXI3 or APB for CPU access to Configuration/Control/Status Registers. The DB-DMAC-MC is tuned as a high-performance DMA Engine.

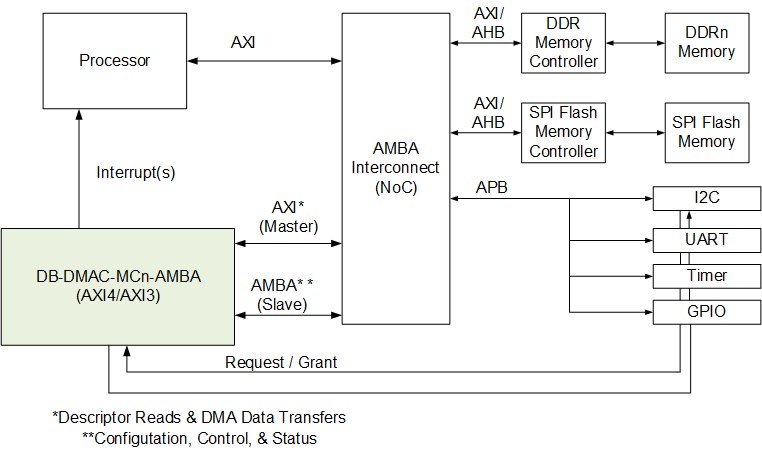

Below is an example System View of the AXI4 DMA Controller IP.

Digital Blocks Family of DMA Controller Engines

In addition to the AXI4 Memory-Map DMA Controller IPs, Digital Blocks offers Multi-Channel Scatter-Gather DMA Controllers that transfers data between AXI4 Memory Map and AXI4-Stream Interfaces (both MM2S and S2MM):

And in addition to AXI4 DMA Controllers, Digital Blocks offers AHB Multi-Channel Scatter-Gather DMA Controllers: