Digital Blocks offers the DB9000 family of programmable Display Controller Verilog IP Cores for systems requiring TFT LCD or OLED panels in their product. The DB9000 TFT LCD / OLED Controller IP Cores are offered with a customer-specific range of features, supporting basic display applications up to optional advanced features.

Display Controller IP

Digital Blocks Display Controller Verilog IP Cores target ASIC/FPGAs design teams with system applications in Medical, Industrial, Aerospace/Defense, Automotive, Computer, Monitor, Consumer, AR/VR Headsets, IoT, Wearables, Signage, Gaming, Broadcasting, & Test Instrumentation. Digital Blocks offers releases containing a variety of optional features from basic baseline display requirements up to advanced display processing features.

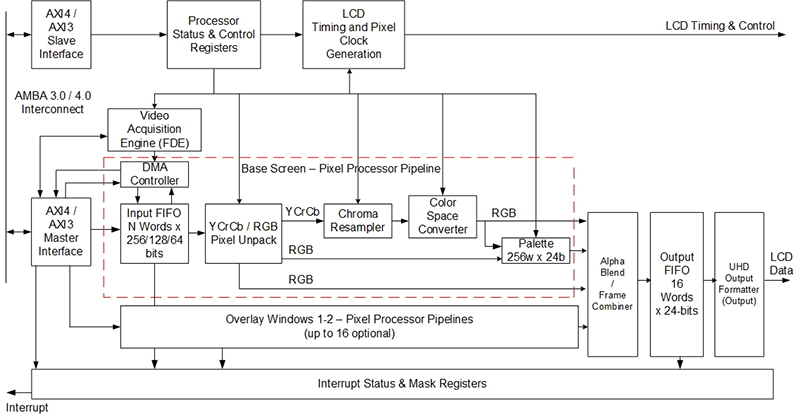

Advanced Display Controller IP Block Diagram

The DB9000AXI4 TFT LCD / OLED Display Controller IP interfaces frame buffer memory and an ARM processor (or any other high-performance processor, such as the RISC-V or MIPS) via the AMBA AXI4 bus fabric to TFT LCD/OLED panels. The DB9000AXI4 contains a 512 / 256 / 128 / 64 or 32-bit AXI4 interface to frame buffer memory controller, and contains a programmable option to drive 1 / 2 / 4 / 8 Port LCD / OLED Panel Interfaces. We optionally offer a LVDS link layer interface as well interfaces to MIPI DSI / DisplayPort / DVI / HDMI / V-by-One Transmitters. The DB9000AXI4 supports a range of display resolutions, with features geared to drive 8K/4K high resolution displays down to 320×240 panels. The DB9000AXI4 supports the AXI4 Specification with higher burst lengths (greater than 16 beats per memory request) and Quality of Service (QoS) capabilities. Available in Verilog, the DB9000AXI4 IP core comes with a comprehensive simulation test suite, Linux driver, Synopsys Design Constraints for synthesis, and a user manual.

The DB9000AXI3 is a slight subset of the DB9000AXI4, supporting the AXI3 interconnect.

The DB9000AHB TFT LCD Display Controller IP interfaces frame buffer memory and an ARM processor via the AMBA AHB bus fabric to TFT LCD panels. Available in Verilog, the silicon-verified DB9000AHB IP core comes with a comprehensive test suite, synthesis scripts, data sheet, and user manual.

The DB9000AHB-Lite offers a AHB-Lite Master interface to frame buffer memory, typically for a point-to-point connection to a multi-port memory controller with the AHB-Lite interface.

The DB9000AVLN TFT LCD Controller IP interfaces frame buffer memory and an Altera® NIOS® II or ARM processor via the Altera Avalon® Bus to TFT LCD panels. Available in Verilog and VHDL, the silicon-verified DB9000AVLN IP core comes with a comprehensive test suite, software driver, synthesis scripts, data sheet, and user manual.

The DB9000AVLN and DB9000AXI are Qsys System Integration Tool and AMPP Approved by Altera

The DB9000AXI-UHD TFT LCD Display Controller IP builds on the AXI4 / AXI3 versions targeting 8K (7680×4320) / 4K (3840×2160) / 2k (1920×1080) panels with added streaming video capabilities.

The DB9000AXI-DCI TFT LCD targets 4K Digital Cinema TFT LCD panels with added features to meet the Digital Cinema Initiative. The DB9000AXI-DCI targets both 2k and 4K Digital Cinema Display requirements, and incorporates UHD / QFHD panel resolutions.